### Low Power Implementation of QRS Detection System

### Suhail Mushtaq Tantray<sup>1</sup>, Ravinder Pal Singh<sup>2</sup>, and Dr Monika Mehra<sup>3</sup>

<sup>1</sup>M. Tech Scholar, Department of Electronics and Communication Engineering, RIMT University, Punjab, India

<sup>2</sup>Technical Head, Department of Research, Innovation & Incubation, RIMT University, Punjab, India

<sup>3</sup>Professor & Head, Department of Electronics and Communication Engineering, RIMT University, Punjab, India

Correspondence should be addressed to Suhail Mushtaq Tantray; suhailmushtaq303@gmail.com

Copyright © 2023 Made Suhail Mushtaq Tantray et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

**ABSTRACT-** This paper proposes a modification of the pre-processing stage of the Pan-Tompkins algorithm. In this paper, the fractional order differentiator now stands in for the integer order differentiator. Since the gain of the fractional order differentiator is lesser than its integer order counterpart, the amplification of the high frequency noise is reduced thus making the design robust to noise. Moreover, all the circuits in this design have been implemented using low-power design techniques so that the system can work with extremely low power consumption. The achievement of the advanced design has been validated by simulations carried out in the HSPICE EDA tool using the TMSC CMOS 130nm process.

**KEYWORDS:** QRS, Pan Tompkins Algorithm, Fractional Order differentiator, ECG Signal, Bandpass filter

### I. INTRODUCTION

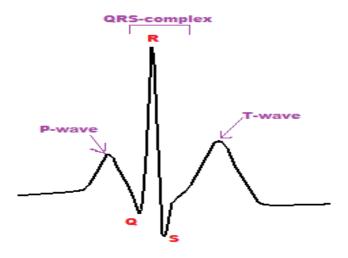

The Electrocardiogram (ECG or EKG) is a technique by which electrical activities of heart are studied from time to time which includes different periods representing several cardiac functions [1]. As shown in Figure 1, the cardiovascular cycle begins with atrial depolarization (P wave), followed by activation of the ventricles (ventricular depolarization) that form QRS complex and eventually recovery (ventricular repol arization) forming a T-wave. ECG analysis provides important information about cardiac function. As most of the power associated with the EKG signal are found at the QRS origin and is also a parameter that is easily detached from the ECG signal, therefore, its accurate detection is very important as it will reflect the patient's health status. Misdiagnosis of QRS can have serious side effects leading to poor diagnosis as well as poor treatment [16].

The discovery of QRS had been the subject of much research for testing for ten years. QRS structures provide important information about cardiovascular function and help diagnose various heart diseases. Although there are a number of algorithms proposed in QRS acquisition documents, the Pan-Tompkins algorithm are the much universally used. The Pan-Tompkins algorithm contain of a pre-processing phase and a detection phase. The pre-processing phase consists of a squarer, bandpass filter, and a differentiator. Various modifications of the Pan-Tompkins algorithm have been suggested in the literature so that QRS detection systems are in line with the current era of low-power technology. In this paper, a low-power

implementation of the pre-processing of the Pan-Tompkins algorithm is presented. In this algorithm, a bandpass filter, differentiator and squarer are used to enhance a QRS signal. The appropriate method of identifying QRS complexes is then used. The traditional Pan-Tompkins algorithm uses an integer order differentiator which amplifies ECG signals and related noise both at a rate of 20dB per decade of frequency. The integer order differentiator is used instead of fractional order differentiator, the magnification can be reduced by a factor equal to the order of the differentiator. Therefore, due to improved audio rejection, we have used a fractional order differentiator instead of the old integer order differentiator. In addition to this, to make the design in line with the modern era of low power design, all blocks are designed using low-power techniques such as log domain and sinh domain methods.

Figure 1: Main parts in a typical ECG beat

### II. PAN-TOMPKINS ALGORITHM

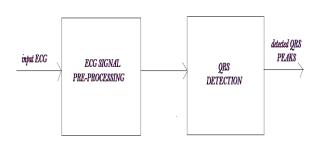

Several methods have been published in the biography for the effective detection of the QRS complex [2-6]. As shown in Fig. 2, any properties of the default QRS detection algorithm can be divided into two categories: pre-processing of the signal and QRS detection [7]. Tasks such as noise filtering, signal amplification etc are performed in the pre-processing phase and adaptive thresholds are used for the detection of the QRS peaks in the next phase.

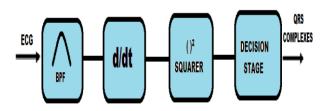

Fig. 3 shows the Functional Block Diagram (FBD) of the Pan-Tompkins algorithm. It includes a bandpass filter for removing noises from various sources. It also diminishes the P-waves and T-waves which have low frequencies. After getting filtered by the bandpass filter, the differentiator receives the filtered signal. The differentiator provides information about the slope of the QRS complex. Then the squarer squares the signal so that the slope is strengthened and wrong positives caused by the T-waves can be avoided.

The Pan-Tompkins algorithm is implemented in assembly language. It operates on either on NSC800 (National Semiconductor) microprocessor or Z80 (Zilog). Integer arithmetic is used for all necessary processing to ensure that the algorithm can run in real-time without consuming a lot of computer resources.

Figure 2: QRS detection structure

Figure 3: FBD of the Pan-Tompkins algorithm

### III. PROPOSED DESIGN AND MODIFICATIONS

As mentioned earlier, the traditional Pan-Tompkins Algorithm uses a integer order differentiator which amplifies ECG signal and the external noise signals both at a rate of 20dB per decade. This process impairs the ability to reject algorithm noise. It is therefore proposed that the integer order differentiator be replaced by a fractional order one. The fractional order differentiator has a much lesser gain than the integer order differentiator. Thus the algorithm will have a much better noise rejection capability due to the reduced amplification of the high frequency noise signals.

Also, to keep pace with the current era of low power design, low power techniques like sinh domain design and log domain design has been used to design all the building blocks. The structure of all such blocks is briefly described in the following subsections.

### A. Design of the Fractional Order Differentiator

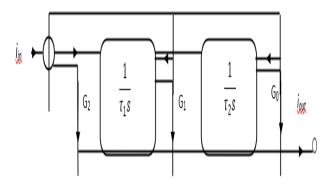

The FLF topology (follow-the-leader-feedback) which has been described in detail in [8] has been used in the design of the fractional order differentiator. Fig. 4 shows the block diagram of the same where the notation xGi denotes the multiplication of the corresponding output of a block by a scalar.

The differentiator's transfer function is provided by:

H(s)

$$= \frac{G_2 s^2 + (G_1/\tau_1)s + G_0/\tau_1 \tau_2}{s^2 + (1/\tau_1)s + 1/\tau_1 \tau_2} \tag{1}$$

Table 1 gives the required values of the gain factors and the time constants.

Fig. 5 shows the implementation of the lossless integrators used in Fig. 4. These have been designed using MOSFETs in subthreshold region.

Figure 4: FBD for realizing fractional-order differentiator of order α using FLF current-mode topology

Table 1: Expressions of time-constants and gain factors for approximating fractional-order differentiator with unity gain frequency ( $\omega o = 1/\tau$ )

| τ1                                           | τ2                                           | $G_0$                                    | $G_1$ | $G_2$                                    |

|----------------------------------------------|----------------------------------------------|------------------------------------------|-------|------------------------------------------|

| $\left(\frac{\alpha_2}{\alpha_1}\right)\tau$ | $\left(\frac{\alpha_1}{\alpha_0}\right)\tau$ | $\left(\frac{\alpha_2}{\alpha_0}\right)$ | 1     | $\left(\frac{\alpha_0}{\alpha_2}\right)$ |

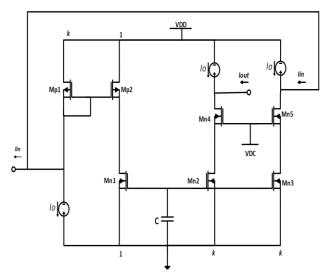

Figure 5: Lossless integrator

For biological signals such as ECG, circuits with large time constants are required since such signals have pretty low frequencies. To fulfill this purpose, current mirrors

### International Journal of Innovative Research in Computer Science & Technology (IJIRCST)

are used. The resulting time constant of the lossless integrator is given by

$$\tau = k \cdot \frac{CnV_T}{I_0} \tag{2}$$

The transfer function of the lossless integrator is given by

$$\frac{I_{out}}{I_{in}} = \frac{1}{\tau \cdot s} \tag{3}$$

There should be a restriction on the range of amplitude of the input signal such that Iin ≤ Iout. Since a class-A integrator is used, this condition is not fulfilled. To overcome this problem, two similar class-A paths are used to design a pseudo-class-AB integrator. This integrator is supplied by output currents of current splitter which are always positive. This configuration is shown in Fig. 6.

Figure 6: Transistor level circuit of a current splitter

Fig. 7 shows the final circuit of the fractional order differentiator. It has been designed by merging the core cells shown in Fig. 5 and Fig. 6.

### B. Design of the Bandpass Filter

The same FLF topology which is shown in Fig. 4 has been used to design a second order bandpass filter. A second order bandpass filter has a transfer function given by

$$H(s) = \frac{(\omega_0/Q)s}{s^2 + (\omega_0/Q)s + \omega_0^2}$$

(4)

where the  $\omega 0$  represents the resonant frequency and Q stands for the Quality factor. These are mathematically given by (5) and (6) respectively

$$\omega_0 = \frac{1}{\sqrt{\tau_1 \tau_2}} \tag{5}$$

$$Q = \sqrt{\frac{\tau_1}{\tau_2}} \tag{6}$$

After comparing the transfer function of the circuit given in Fig. 4 with (4), we conclude that we can design the bandpass filter provided we select the values of the scaling factors as following

$$G0 = 0$$

,  $G1 = 1$  and  $G2 = 0$

On substitution of the values of  $\tau i$ , the resonant frequency  $(\omega 0)$  and the quality factor (Q) are calculated as

$$\omega_0 = \frac{I_0}{nV_T} \frac{1}{\sqrt{C_1 C_2}} \tag{7}$$

$$\omega_0 = \frac{I_0}{nV_T} \frac{1}{\sqrt{C_1 C_2}}$$

$$Q = \sqrt{\frac{C_1}{C_2}}$$

(8)

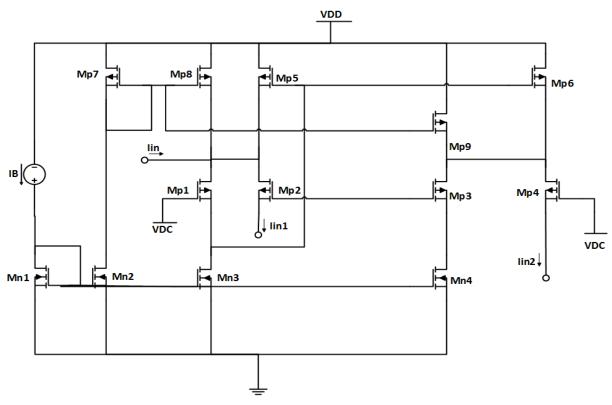

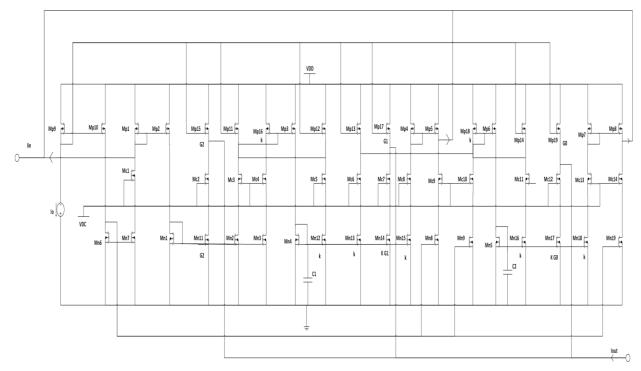

Figure 7: Realization of fractional order differentiator of order α

### C. Design of the Current Squarer

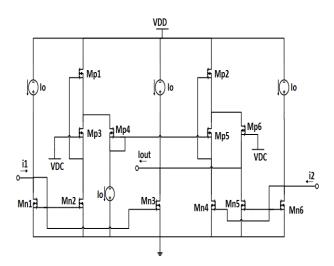

A four-quadrant multiplier is used to design the current squarer. Such a multiplier is described in detail in [9]. Fig. 8 shows the circuit of such a multiplier.

The output of the multiplier is given by:

$$I_{out} = \frac{-I_1 * I_2}{I_0}$$

Putting I1 = I2 we can operate it as a current squarer.

## IV. SIMULATION AND COMPARISON RESULTS

HSPICE simulation software was used to evaluate the performance of the system. TSMC 130 nm CMOS file was employed. VDD and VDC were set to 0.5 V and 300 mV, respectively, to get the dc bias voltage. DC current i.e. I0 was equal to 300pA.

# A. Performance of the Extraordinary Order Differentiator

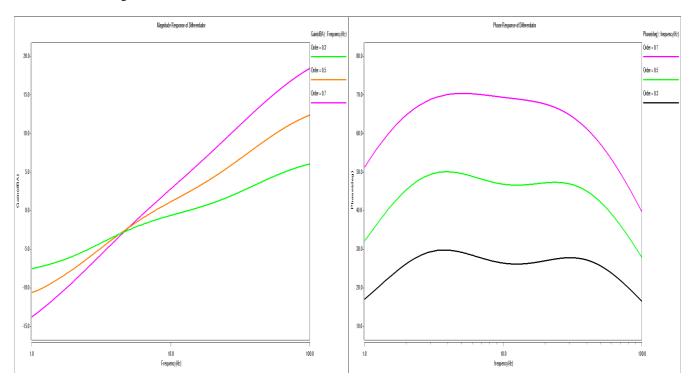

To check working of the extraordinary order differentiator, a differentiator of three different orders i.e.  $\alpha=0.3$ ,  $\alpha=0.5$  and  $\alpha=0.7$  was designed. f0=10 Hz was chosen as the differentiator's unity gain frequency. The equations given in Table 1 were used to find the capacitances of the capacitors used. For the purpose the value of k was set as 6.

Table 2 shows these values along with the scaling factors and Table 3 shows the aspect ratios of the transistors used in the system.

The magnitude output of the extraordinary order differentiator of the above mentioned orders is shown in Fig. 9 along with the respective phase responses.

Figure 8: Topology of the four-quadrant multiplier

Table 2: Values of capacitors and scaling factors for fractional-order differentiator of order  $\alpha$

| Order (a) | C <sub>1</sub> | $\mathbb{C}_2$ | $G_0$ | $G_1$ | $G_2$ |

|-----------|----------------|----------------|-------|-------|-------|

| 0.3       | 3.55<br>pF     | 62.16<br>pF    | 0.4   | 1     | 2.5   |

| 0.5       | 2.36<br>pF     | 47.2 pF        | 0.2   | 1     | 5     |

| 0.7       | 1.32<br>pF     | 35.52<br>pF    | 0.085 | 1     | 11.7  |

Table 3: Transistors used in Fig. 7 and their aspect ratios

| Transistors                                           | Aspect Ratio |

|-------------------------------------------------------|--------------|

| $M_{\rm n1}-M_{\rm n5}$                               | 5µm/10µm     |

| $M_{n6} - M_{n10}$                                    | 4μm/10μm     |

| $M_{c1}-M_{c14}$                                      | 10μm/1μm     |

| $\mathbf{M}_{\mathrm{p}1} - \mathbf{M}_{\mathrm{p}8}$ | 2μm/4μm      |

| $M_{p9} - M_{p14}$                                    | 4μm/5μm      |

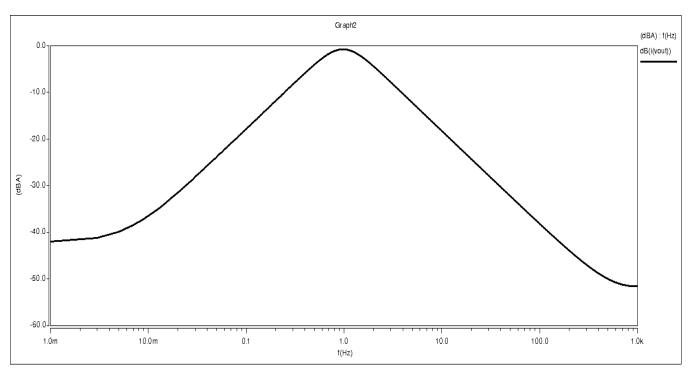

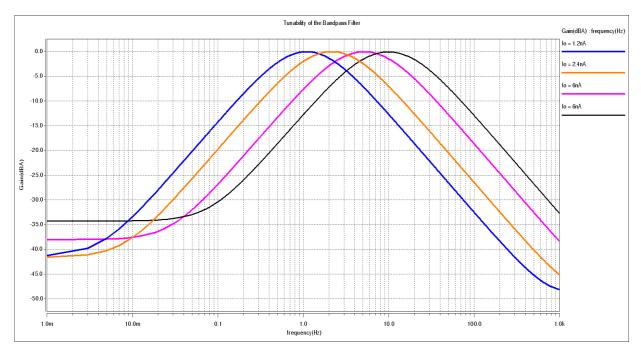

### B. Performance of the Bandpass Filter

The bandpass filter was first designed having centre frequency 1 Hz. Its simulated frequency output is shown in Fig 10. The designed bandpass filter are highly tunable as it can be easily tuned to different centre frequencies simply by altering the value of I0. This tunability is shown mathematically in equation (7) and is shown in its simulated form in Fig. 11.

### C. Performance of the Current Squarer

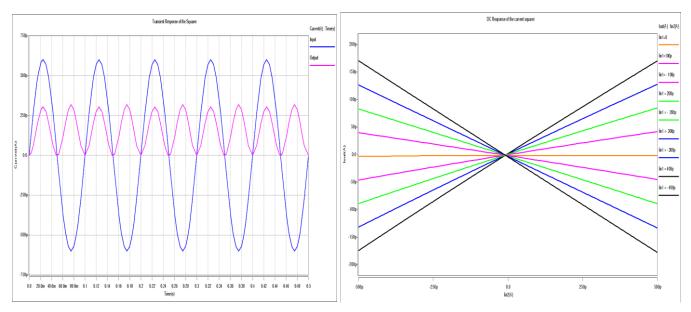

To evaluate the performance of the current squarer (four-quadrant multiplier), a sine wave was fed to both the inputs. Its transient response was simulated and are depicted in Fig. 12. Fig. 12 also presented the dc analysis of the squarer. For dc analysis, the input Iin2 was varied from -500pA to +500pA and the input Iin1 was kept constant.

Figure 9: Magnitude response (left) and phase response (right) of the fractional order differentiation of order 0.5, 0.3 and 0.7

Figure 10: Frequency response of the designed bandpass filter

Figure 11: Tunability of the bandpass filter

Figure 12: Transient response (left) and DC response (right) of the four-quadrant multiplier

### D. Overall System Achievements

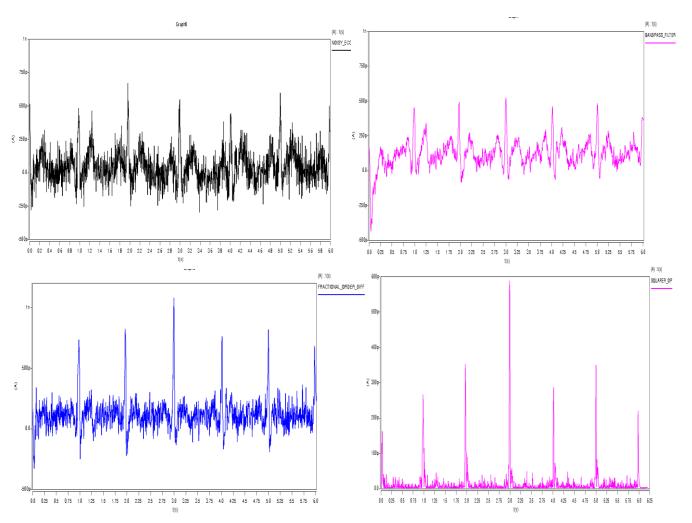

The achievement of the designed system was mainly evaluated for the noisy environments. For this purpose Gaussian noise was added in MATLAB to a clean ECG to construct a noisy ECG as shown in Fig. 14(a). SNR (signal-to-noise ratio) of the resulting ECG was 0 dB.

When the mentioned noisy ECG is fed at the input, the outputs of the system at various stages are shown in Fig. 14. Fig. 14(b) depicts the output of the bandpass filter. This figure clearly shows that the filter efficiently attenuates the high frequency noises. The output of the extraordinary order differentiator is shown in Fig. 14(c) while the Fig. 14(d) shows the final output which is same as the output of

the multiplier. The final output shows that the system efficiently occurs the QRS peaks regardless of presence of distortions in the ECG signal.

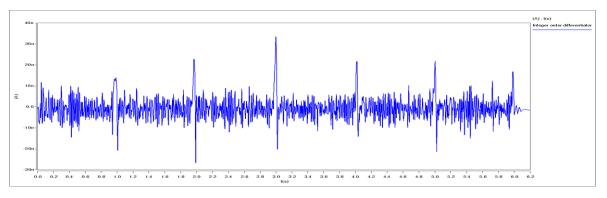

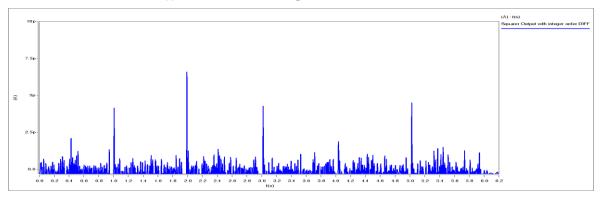

Fig. 15 shows the results of the same system when the extraordinary order differentiator is replaced by the integer order differentiator in order to show the comparisons. The integer order differentiator also amplifies the noises thereby making false detections or missed beats in the noisy environments. This situation can be also seen in Fig. 15(a) which shows the output of the integer order differentiator. Hence it can be concluded that the incorporation of the extraordinary order differentiator into the system improves its performance in the noisy environments.

Figure 13: Outputs obtained at various stages of the system with noisy ECG as input

(a) Response of the integer-order differentiator

(b) Response of the squarer after using the integer order differentiator

Figure 14: Performance of the algorithm when an integer order differentiator is used

### V. CONCLUSIONS

In this paper the low power utilization of the QRS detection system has been discussed. The detection system has been implemented by using Pan-Tompkins algorithm with the integer order differentiator being replaced by the extraordinary order differentiator. The design of the extraordinary order differentiator has been discussed in detail. In addition, the design of other required blocks such as the bandpass filter and the current squarer has also been discussed. The simulation results show that the design clearly detects all the QRS complexes. Further all the blocks have been designed using the low power techniques such as the log-domain technique and the sinh-domain technique in order for the design to be compatible with the contemporary low power era. As a consequence the design can operate at very low power with a voltage of 500 mV and currents of the order of pico-amperes. This makes the design suitable for portable applications such as ambulatory and mobile devices. More over by the utilization of fractional order differentiator, the system becomes more immune to noises. The same has also been shown by simulation results by exciting the system with a noisy ECG. It is also compared with the traditional integer order differentiator and considerable improvement in its performance can be clearly seen. The detection system is also highly efficient in terms of area requirements. The whole system can be implemented by the utilization of just 120 transistors.

#### CONFLICTS OF INTEREST

The authors declare that they have no conflicts of interest.

### **REFERENCES**

- L. S. Rnmo and P. Laguna, Electrocardiogram (ECG) Signal Processing, Wiley Encyclopedia of Biomedical Engineering, John Wiley & Sons, Inc., (2006).

- [2] J. Pan and W. J. Tompkins, A real-time QRS detection algorithm. IEEE Transactions on Biomedical Engineering 32, 230 (1985)

- [3] P. S. Hamilton and W. J. Tompkins, Quantitative investigation of QRS detection rules using the MIT/BIH Arrhythmia database. IEEE Transactions on Biomedical Engineering 33, 1157 (1986).

- [4] A. Martínez, R. Alcaraz, and J. Rieta, Application of the phasor transform for automatic delineation of single-lead ECG fiducial points. Physiological Measurement 31, 1467 (2010).

- [5] B. Kohler, C. Hennig, and R. Orglmeister, The principles of software QRS detection. IEEE Engineering in Medicine and Biology Magazine 21, 42 (2002).

- [6] N. Arzeno, Z. Deng, and C. Poon, Analysis of first-derivative based QRS detection algorithms. IEEE Transactions on Biomedical Engineering 55, 478 (2008).

- [7] Hu, Y.H., Tompkins, W.J., Urrusti, J.L., and Afonso, V.X., Applications of artificial neural networks for ECG signal detection and classification. Electrocardiology, 1993; 26 (Suppl.): 66-73.

- [8] Q. Xue, Y. H. Hu, and W. J. Tompkins, "Neural-network-based adaptive matched filtering for QRS detection," IEEE Trans. Biomed. Eng., vol. 39, pp. 317-329, 1992.

- [9] G. Vijaya, V. Kumar, and H.K. Verma, "ANN-based QRS-complex analysis of ECG," J. Med. Eng. Technol., vol. 22, no. 4, pp. 160-167, 1998.

- [10] G. Tsirimokou and C. Psychalinos, Ultra-low voltage fractional order differentiator and integrator topologies: An

- application for handling noisy ECGs. Analog Integrated Circuits and Signal Processing 81, 393 (2014).

- [11] G. Vijaya, V. Kumar, and H.K. Verma, "ANN-based QRS-complex analysis of ECG," J. Med. Eng. Technol., vol. 22, no. 4, pp. 160-167, 1998.

- [12] Farooq A. Khanday, Evdokia Pilavaki, and Costas Psychalinos," Ultra Low-Voltage Ultra Low-Power Sinh-Domain Wavelet Filer for Electrocardiogram Signal Analysis", Journal of Low Power Electronics Vol. 9, 1–7, 2013

- [13] Q. Xue, Y. H. Hu, and W. J. Tompkins, "Neural-network-based adaptive matched filtering for QRS detection," IEEE Trans. Biomed. Eng., vol. 39, pp. 317-329, 1992.

- [14] Krishna, B. (2011). Studies on fractional order differentiators and integrators: A survey. Signal Processing, 91(3), 386–426.

- [15] J. Fraden and M.R. Neumann, "QRS wave detection," Med. Biol. Eng. Comput., vol. 18, pp. 125-132, 1980.

- [16] Farhad Ahmad Mir, Ravinder Pal Singh, Dr. Monika Mehra. "Separating FECG from MECG and Analyzing Fetal Heart Rate Using Pan Tompkins algorithm", International Journal of Innovative Research in Computer Science & Technology (IJIRCST) ISSN: 2347-5552, Volume-10, Issue-1, January 2022.